Η Quotidien économique de Taiwan il prétend que le TSMC a réalisé une importante découverte interne pour son stockage définitif technologie de lithographie 2 nm.

ΣSelon la publication, cette étape permet à TSMC de est optimiste quant à la mise en place d'une production précoce "Risk Production" 2 nm en 2023.

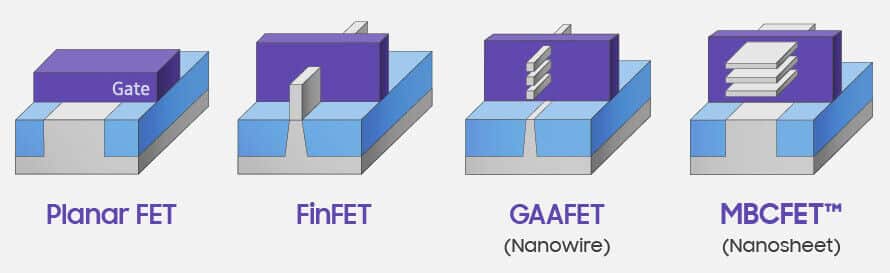

Les rapports qui TSMC abandonne la technologie FinFet pour un nouveau transistor à effet de champ à canaux multiples (MBCFET) basé sur la technologie Gate-All-Around (GAA). Cette importante découverte arrive un an après la création d'une équipe indoor par TSMC, dont le but était d'ouvrir la voie au développement de la lithographie 2 nm.

La technologie MBCFET étend l'architecture GAAFET en prenant le transistor à effet de champ Nanowire et en le « diffusant » pour devenir une nanofeuille. L'idée principale est de réaliser le transistor à effet de champ en XNUMXD.

Ce nouveau transistor semi-conducteur à oxyde métallique complémentaire peut améliorer le contrôle des circuits et réduire les fuites de courant. Cette philosophie de conception n'est pas exclusive à TSMC - Samsung prévoit de développer une variante de cette conception dans leur technologie de lithographie 3 nm.

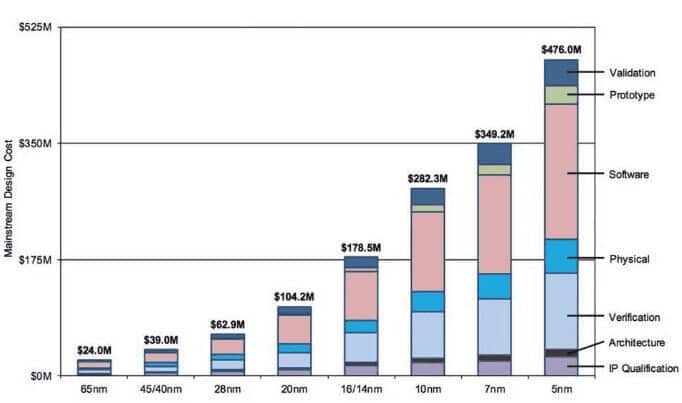

Comme d'habitude, une réduction supplémentaire de l'échelle de fabrication des puces a un coût énorme. En particulier, le coût de développement de la lithographie 5 nm a déjà atteint 476 millions de dollars, tandis que Samsung précise que la technologie GAA de 3 nm coûtera plus de 500 millions de dollars. Bien sûr, le développement de la lithographie 2 nm, dépassera ces montants…

N'oubliez pas de le suivre Xiaomi-miui.gr à Google Actualités pour être informé immédiatement de tous nos nouveaux articles !

N'oubliez pas de le suivre Xiaomi-miui.gr à Google Actualités pour être informé immédiatement de tous nos nouveaux articles !